Conference and Exhibition - 14-18 March 2022

Call for Papers

Scope of the Event

The 25th DATE conference and exhibition is the main European event bringing together designers and design automation users, researchers and vendors as well as specialists in hardware and software design, test and manufacturing of electronic circuits and systems. DATE puts strong emphasis on both technology and systems, covering ICs/SoCs, emerging technologies, embedded systems and embedded software.

Structure of the Event

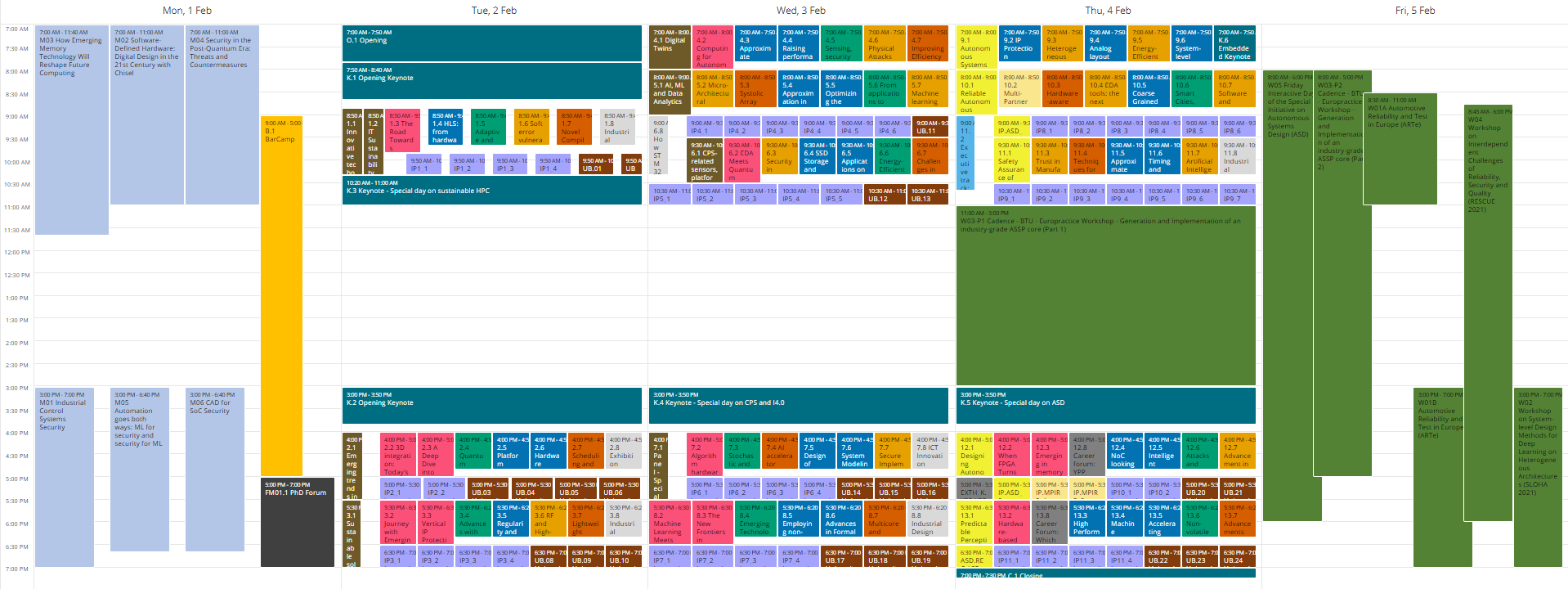

The multi-day event consists of a conference with regular papers, panels, hot-topic sessions, tutorials, workshops, special focus days and executives. The scientific conference is complemented by various commercial showcases presenting the state-of-the-art in design and test tools, methodologies, IP and design services, reconfigurable and other hardware platforms, embedded software and (industrial) design experiences from different application domains, such as automotive, wireless, telecom and multimedia applications. The event will host the young people programme, the university fair and multi-partner projects dissemination on innovative research activities fostering the networking and the exchange of information on relevant issues, recent research outcomes and career opportunities.

More details are available on the DATE website: www.date-conference.com.

Areas of Interest

Within the scope of the conference, the main areas of interest are: design automation, design tools and hardware architectures for electronic and embedded systems; test and dependability at system, chip, circuit and device level for analogue and digital electronics; modelling, analysis, design and deployment of embedded software and cyber-physical systems; application design and industrial design experiences.

Topics of interest include, but are not restricted to:

- System Specification and Modelling

- System-level Design Methodologies and High-Level Synthesis

- System Simulation and Validation

- Formal Methods and Verification

- Design and Test for Analogue and Mixed-Signal Circuits and Systems, and MEMS

- Design and Test of Secure Systems

- Network on Chip and Communication-Centric Design

- Architectural and Microarchitectural Design

- Low-power, Energy-efficient and Thermal-aware Design

- Approximate Computing

- Reconfigurable Systems

- Logical and Physical Analysis and Design

- Emerging Design Technologies for Future Computing

- Emerging Design Technologies for Future Memories

- Power-efficient and Sustainable Computing

- Robotics and Industry 4.0

- Automotive Systems and Smart Energy Systems

- Augmented Living and Personalized Healthcare

- Secure Systems, Circuits and Architectures

- Self-adaptive and Learning Systems

- Applications of Emerging Technologies

- Modelling and Mitigation of Defects, Faults, Variability and Reliability

- Test Generation, Test Architectures, Design for Test, and Diagnosis

- Microarchitecture-Level Dependability

- System-Level Dependability

- Real-time and Dependable Systems

- Embedded Systems for Deep Learning

- Model-based Design, Verification and Security for Embedded Systems

- Embedded Software Architectures, Compilers and Tool Chains

- Cyber-Physical Systems Design

DATE 2022 will host for the third year a two-day initiative on Autonomous Systems Design: Fueled by the progress of artificial intelligence, autonomous systems become more and more integral parts of many Internet-of-Things (IoT) and Cyber-Physical Systems (CPS) applications, such as automated driving, robotics, avionics and industrial automation. Autonomous systems are self-governed and self-adaptive systems that are designed to operate in an open and evolving environment that has not been completely defined at design time. This poses a unique challenge to the design and verification of dependable autonomous systems. The DATE Initiative on Autonomous Systems Design will include peer-reviewed papers, invited contributions and interactive sessions addressing these challenges.

Submission of Papers

All papers must be registered by Sunday, 12 September 2021 AoE (title, abstract and co-authors), the final version of the paper to be submitted by Sunday, 19 September 2021 AoE (firm deadline) via: https://www.date-conference.com/

Papers can be submitted either for standard oral presentation or for interactive presentation.

The Program Committee also encourages proposals for Special Sessions, Tutorials, Friday Workshops, University Booth Demonstrations, PhD Forum and Exhibition Theatre.

Chairs

General Chair:

Cristiana Bolchini, Politecnico di Milano, IT

E-mail: cristiana [dot] bolchini polimi [dot] it (cristiana[dot]bolchini[at]polimi[dot]it)

polimi [dot] it (cristiana[dot]bolchini[at]polimi[dot]it)

Programme Chair:

Ingrid Verbauwhede, KU Leuven, BE

E-mail: Ingrid [dot] verbauwhede kuleuven [dot] be (Ingrid[dot]verbauwhede[at]kuleuven[dot]be)

kuleuven [dot] be (Ingrid[dot]verbauwhede[at]kuleuven[dot]be)

Conference Organisation

c/o K.I.T. Group GmbH Dresden

Bautzner Str. 117–119, 01099 Dresden, DE

Phone: +49 351 65573-137

E-mail: date kitdresden [dot] de (date[at]kitdresden[dot]de)

kitdresden [dot] de (date[at]kitdresden[dot]de)

Share this page on social media

General Chair

General Chair Programme Chair | Track D | Design, Methods and Tools Chair

Programme Chair | Track D | Design, Methods and Tools Chair

Conference Organisation | Exhibition and Sponsorship

Conference Organisation | Exhibition and Sponsorship